1. 引言

物联网,智能汽车,云计算在我们生活中已经耳熟能详,随着FPGA的更新进步,在各类电子科技中不断发力,让我们的生活变得更加智能和便捷。下面给大家介绍一下来自Intel的FPGA Arria 10以及明德阳研发的一款Arria 10的核心板电路设计。

2. Arria 10 FPGA

来自Intel Arria10 FPGA是目前市场上性能最好的,采用20纳米技术,性能比竞争器件高出一个速率等级。Arria 10 FPGA和SoC功耗比前一代FPGA和SoC低40%,具有业界唯一的硬核浮点数字信号处理(DSP)模块,其速率高达每秒1,500giga 次浮点运算。Arria10采用可编程功耗技术,智能电压ID技术等,使电路的器件功耗大大降低,同时通过集成节省了电路板空间100多万个逻辑单元(LE),密度比前一代中端器件高出2倍。这些集成特性满足了很多行业的应用需求,包括,通信、国防、高性能计算和医疗等。

3. Arria10核心板设计

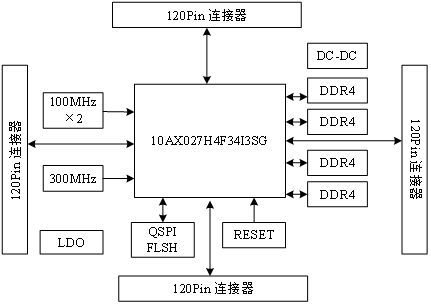

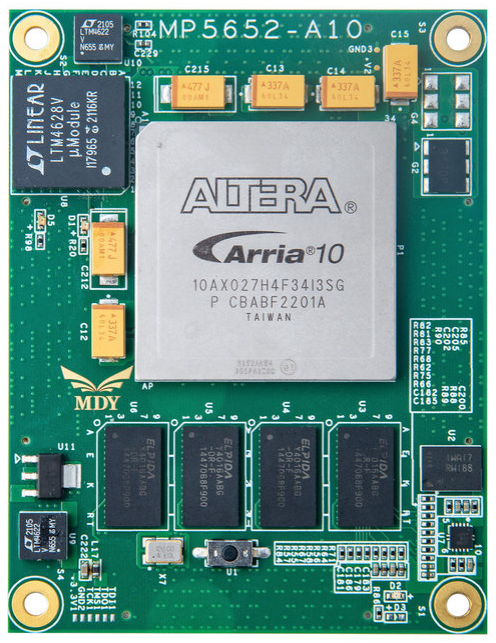

今天分享的由明德阳研发的Arria 10 FPGA核心板,命名为MP5652,采用Intel公司Arria-10 GX系列的10AX027H4F34I3SG作为主控制器,核心板上采用4个0.5mm间距120Pin 镀金连接器与母板连接,核心板四个脚放置了4个3.5mm固定孔,此孔可以与底板通过螺丝紧固,确保了在强烈震动的环境下稳定运行。这款核心板使用Intel的Arria 10 GX芯片的解决方案,在FPGA 芯片的HP 端口上挂载了4片DDR4存储芯片,每片DDR4 容量高达4Gb(256Mb × 16) 字节,每片16bit组成64bit 位的数据位宽。1片1GB 的QSPI FLASH 芯片用来静态存储FPGA 芯片的配置文件或者其它用户数据。核心板结构尺寸为65(mm)× 85(mm),沉金工艺。供电电压范围5—12V都可以工作。整个开发系统的结构如图1所示,实物图如图2所示。

图1 核心板结构图

图2 核心板实物图

图2 核心板实物图

2.1主要电路设计

2.1.1 FPGA芯片选择

核心板使用的是Intel公司的Arria-10 GX芯片,芯片型号可选10AX027H4F34I3SG。速度等级为3,温度等级为工业级。此型号为FFG1152封装,1152个引脚,引脚间距为1.0mm。FPGA主要参数如表1。

表1 FPGA参数表

名称 | 详细参数 |

Pin(I/O) | 1152 |

Logic Elements (LE) (K) | 270 |

ALM | 101,620 |

Register | 406,480 |

Memory M20K (Kb) | 15,000 |

DSP Block | 830 |

18 x 19 Multiplier | 1660 |

Transceiver | 124个, 17.4 Gbps |

GPIO | 384 |

LVDS Pair | 168 |

速度等级(Speed Grade) | -3 (Mid) |

温度等级(Temperature Grade) | I (工业级) |

2.1.2 DDR4 SDRAM

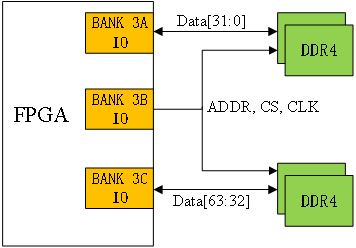

DDR4 SDRAM(Double-Data-Rate Fourth Generation Synchronous Dynamic Random Access Memory),是一种高带宽的计算机存储器规格。它属于SDRAM家族的存储器产品,提供了相较于DDR3 SDRAM更高的运行性能与更低的电压,是现时最新的存储器规格。MP5652开发板上配有四片Micron Technology的4 Gb的DDR4芯片,型号为EDY4016AABG-DR-F-D。每片DDR4 SDRAM数据位宽为16 bit,共组成64 bit的数据总线宽度。因为4片DDR4芯片连接到FPGA的BANK3A、BANK3C、BANK3D的接口上,DDR4 SDRAM的最高运行速度可达1200 MHz(数据速率2400 Mbps)。DDR4的接口的设计示意图如图3所示。DDR4 的硬件设计需要严格考虑信号完整性,电路及PCB 设计已经充分考虑了匹配电阻/终端电阻,走线阻抗控制,走线等长控制,以确保DDR4 稳定工作。

图3 DDR4的接口设计

2.1.3 QSPI Flash

板上配有一片1Gb大小的Quad-SPI Flash芯片,型号为MT25QU01GBBB8E12-0SIT,它使用1.8V CMOS电压标准。由于QSPI FLASH的非易失特性,在使用中,它可以存储FPGA的配置Bin文件以及其它的用户数据文件。

2.1.4 核心板时钟

MP5652核心板为了准确适配不同用途的时钟频率,板载多个时钟源。其中包括100MHz的系统时钟源510KBA100M000BAG CMOS晶振,125MHz的Transceiver差分时钟源SiT9102晶振, 300 MHz的DDR4的外部差分时钟源SiT9102晶振。SiT9102是一款高精度、超低相噪的晶振,非常适合作为高速信号处理系统的时钟源。最后,为了缩短大容量FPGA芯片的下载配置时间,板卡还配有100MHz的初始化时钟源510KBA100M000BAG CMOS晶振,连接CLKUSR 引脚,用户可以配置使用该时钟,配合QSPI×4模式,从而大大提高FPGA的配置效率。

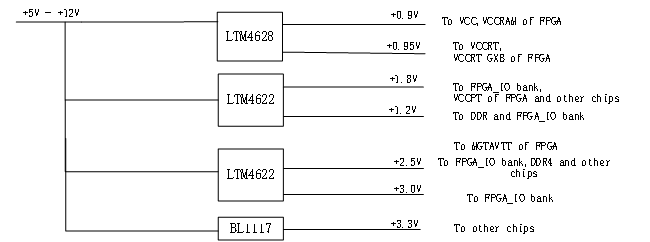

2.1.5核心板电源

核心板集成电源管理,+5—+12V电源输入通过TI 电源芯片LTM4628 分别产生0.9V和0.95V的两路电源,其中一路为FPGA的核心提供稳定的电源,另一路为Transceiver GXB的VCCRT提供稳定的电源,LTM4628输出电流高达8A,满足FPGA电流需求。+5—+12V电源输入通过TI 电源芯片LTM4622分别产生+1.2V、+1.8V、+2.5V、+3.0V电压,单片LTM4622有两路电源输出,所以需要2片LTM4622。LTM4622为FPGA其他电源、DRR4、晶振、FLASH等供电。+5V电压经过BL1117转换为3.3V直流,为3.3V晶振提供电压。另外电源上电顺序按官方时序要求进行了控制。 核心板供电架构如图4所示。

图4 电源供配电分布

2.1.6 FPGA BANK接口电平选择

板上对外的BANK分别为BANK2A/2J/2K/3D, 这些BANK的IO均支持1.8V/1.2V两种电平可调,默认电平为1.8V。BANK2L, 这些BANK的IO均支持3.0V/2.5V/1.8V/1.2V四种电平可调,默认电平为3.0V。如果需要更换电平,只需要更换对应位置磁珠即可实现调整,核心板BANK电平调节磁珠位置。

4. 总结

通过以上描述,我们能够清晰看到这个核心板所含有的接口和功能。核心板一共扩展出4个高速扩展口,使用4个120Pin的板间连接器和母板连接。这款核心板的4个板对板连接器扩展出了244个IO,也扩展出了16对高速收发器GTX接口。对于需要大量IO的用户,此核心板将是不错的选择。另外,BANK2A、BANK2K、BANK2J、BANK3D的全部IO的电平可以通过更换核心板上的磁珠来修改,满足用户对+1.8V、+1.2V电平接口的需求,默认+1.8V;BANK2J的全部IO的电平也可以通过更换核心板上的磁珠来修改,满足用户对+3.0V、+2.5V、+1.8、+1.2V电平接口的需求,默认+3.0V。IO连接部分,同一个BANK管脚到连接器接口之间走线做了等长和差分处理,对于二次开发来说,非常适合。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。